アナログ回路を勉強する回路設計のホームページ:http://kaironohanashi.main.jp/index.htmlです。

Comparator Circuits:コンパレータ設計手順の例1

どうでしたでしょうか?素敵な回路が思いつきましたか?

では、もう一度要求仕様を挙げてみます。

<要求仕様>

(10V以上か10V以下でコンパレートしたい) コ

ンパレータ出力の電圧は3V以下にしたい、

ただし、出力電圧はHを2.5V以上、Lを0.5V以下で出力したい。

まずは、簡単のために、コンパレータの速度は問わない 。

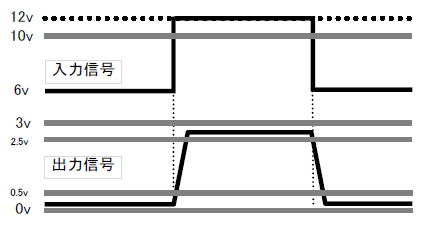

これを波形で表すと

Fig.1 例1の要求仕様

例えば上記仕様を満たす回路は、 何通りもの回路で実現できます。つまり、答えは1つではありません。では、このあと作者が考える場合で、この仕様を満たす 最も簡単な形式と手順を説明してみましょう。

Contents:仕様を満たす簡単なコンパレータ回路設計例1

<作者流の考え方の例>

コンパレータ回路の電源電圧が12Vなので この回路を簡単に実現するためには12V以上の素子耐圧がある トランジスタを選択します。

↓

入力信号を基準電圧10Vで比較する必要があるので 回路の入力部は差動対を選択します。入力信号が6v〜12vまで振れるので、 入力差動対の動作範囲は6v〜12vまでは最低限必要です。つまり、電源電圧12vに対し、入力信号は最大12v入るので

差動対はNPNトランジスタを使ったダーリントン構成を選択します。

↓

これで入力信号を10vでコンパレートする入力段は決定しました。

↓

次にコンパレータ出力は、3Vの電源で、 かつ 出力電圧はHを2.5V以上、Lを0.5V以下で出力なので、 一番簡単に実現するには、 出力の電源電圧3Vに抵抗でプルアップする形の

エミッタ接地回路にします。これで入力段と出力の形式は決定です。

↓

では、次に入力差動対から出力部のエミッタ接地回路への中継を考えます。一番簡単なのは、差動対の負荷を抵抗しに、 その抵抗の電圧降下をPNPトランジスタのベースで受ける形式です。そのPNPもエミッタ接地形式にし、

コレクタ端子を抵抗負荷にします。

↓

PNPのエミッタ接地の出力を 出力段のエミッタ接地のベースに入力します。これで回路形式は完成です。抵抗値や電流値は、その回路の許容回路電流値と 素子能力で決定していきます。

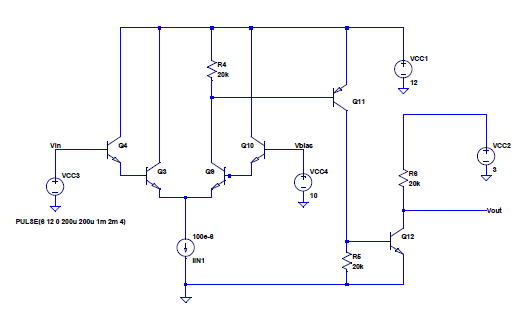

以上の考え方で組み立てた簡単な回路例は次のようになります。

(スピードなど、難しいことは考えていないので定数は任意の定数です。)

Fig.2 設計した回路例

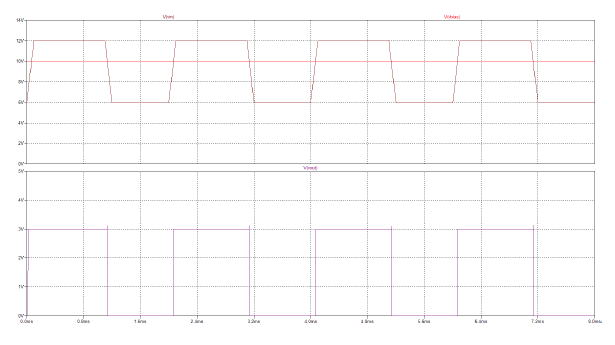

次にこの回路が要求仕様を満たすかシミュレーションで確認してみましょう。ただし、切り替わりが分かりやすいように入力6-12vパルスの立ち上がりと

立下りは若干なまらせています。

Fig.3 設計した回路のシミュレーション結果

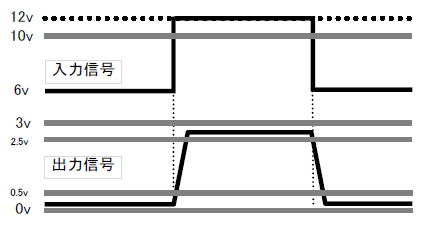

Fig.4 要求仕様特性

Fig.3とFig.4を比較すると要求仕様を満たしていることが分かります。

以上、簡単な例を使って回路設計手順を考えてみましたが これ以外にもさまざまな方法で実現出来ますので 皆さんいろいろな形式を考えてみてください。

でもこの手順を読んで分かると思いますが、 設計する場合、重要なのは、 如何に基本コンポーネントを理解し、使えるかということです。また、自分の中で、回路の引き出しを如何に多く持っているかということです。

コンパレータの基本回路設計を勉強したい方はこちらへ

コンパレータの回路設計をもう1つやってみたい方はこちらへ

このサイトの内容は趣味で勉強してきたことを応用し、綴っているページです。一般的なことを書いているつもりであり、広告などございますが、あくまで趣味で作っているサイトです。また、特許や商標などは十分調査できていません。また、そういった権利を侵害するつもりもございませんので、万が一そういった場合は削除させていただきますので連絡いただきたいです。また、本ページの内容は実際の動作などを保証するものではございません。使っているツールなども趣味の範囲で使っているため、商用などで利用する場合は注意していただきたいです。また、参考文献などはリンクで表示させていただいております。上記内容につきましては、あらかじめご了承ください。