アナログ回路を勉強する回路設計のホームページ:http://kaironohanashi.main.jp/index.htmlです。

Transistor Circuits:エミッタ接地回路の基本5

今回は、エミッタ接地回路の回路例を示し、基本的な内容をまとめていきます。

Contents:解説1、 エミッタ接地回路の例

よくあるエミッタ接地回路について考えていきます。回路を考える前に、もう一度ポイントを整理しておきます。増幅したい入力信号が、その回路の適切なバイアスポイントを外れると、出力電圧は、電源付近や、0V付近に張り付いてしまうなど、うまく増幅器として、成り立りたたないことは、前のページで、説明しました。

では、入力する信号のDC成分と入力回路のバイアスポイントを一致させるには、どうすればよいのでしょうか?

ここで考えたいのは、入力する信号のDC成分を取り除き、AC成分だけを入力回路のバイアスポイントに乗せられないか?ということです。この特性を実現できるのは、ハイパスフィルタです。ハイパスフィルタは、高い周波数のみ通過させるフィルタです。これを考えてみましょう。

Fig.1 ハイパスフィルタの基本形

この回路のカットオフ周波数は、fp=1/2πCRで決定されます。これを入力部で使うためには、どうすればよいでしょうか?このハイパスフィルタの出力部には、抵抗があります。つまり、エミッタ接地回路のバイアス電圧を生成する抵抗分割にコンデンサを接続すれば、同じ構成ができます。結果、以下のようになります。

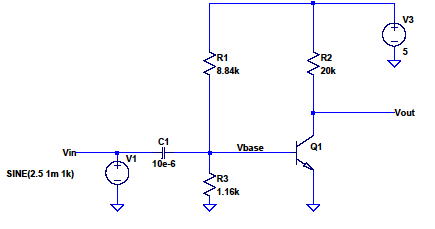

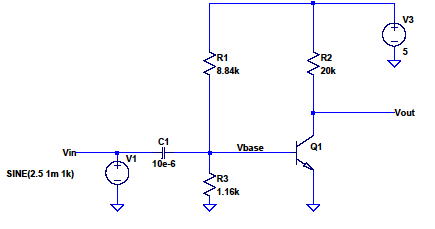

Fig.2 ディスクリート回路でよく見るエミッタ接地回路

次に、この回路のカットオフ周波数を考えます。トランジスタQ1のベース電流を無視して考えると、R3は、対GNDに接続されていることと、R1は、AC的に電源に接地されるので、Fig.1のCが、C1に相当し、RがR1//R3に相当します。

カットオフ周波数は、

fp=1/2πC1(R1//R3)となります。

Contents:解説2、 エミッタ接地回路の例

Fig.3 ディスクリート回路でよく見るエミッタ接地回路

では、実際に回路の計算を行ってみます。

1、ベース電圧Vbase ベース電圧は、R1とR3による抵抗分割で決まるので、 Vbase=5v×1.16kΩ/(8.84kΩ+1.16kΩ)=0.58v

となります。

2、ゲインを求めます。

ここで、β=120、アーリー電圧=VA=100vとします。Vbase電圧の設定により、出力Voutが電源電圧の1/2、つまり2.5vで振れるとすると、

Q1のコレクタ電流Icは、

Ic=2.5v÷20kΩ=125uA となります。

出力インピーダンスは、ro=(VA+Vce)/Icなので、Vceが十分小さいとおくと、

roQ1=VA/Ic=100v/125uA=800kΩ となります。

ゲインは、Av=-gm×(roQ1//R2)なので、

Av=-(125uA/0.026)×(800kΩ//20kΩ)=-93.75倍(39.4dB) となります。

尚、上記で、roの式とAvの式を出してきましたが、別のページで詳しく説明するため、今は、こういうものだと考えておいてください。

3、ハイパスフィルタのカットオフ周波数 fp=1/2πC1(R1//R3)より、

fp=1/2π/10u(8.84kΩ//1.16kΩ)=15.5Hz

今回入力する信号を1kHzとすると、15.5Hzでは、問題なく信号を通過できます。

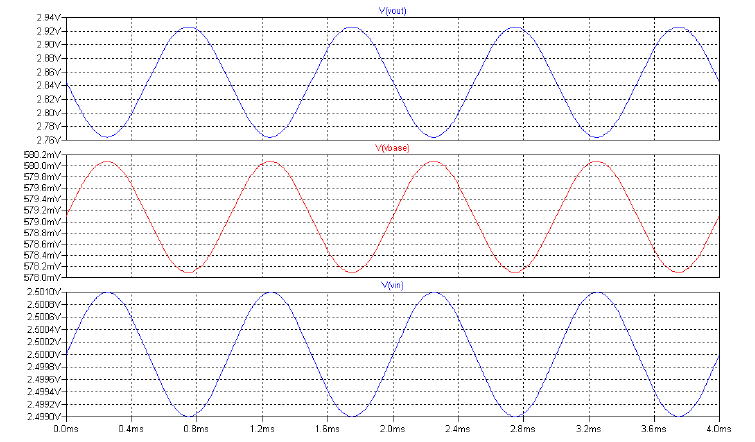

では、実際に信号を入力して確認してみます。確認結果をFig.4に示します。

Fig.4、 Fig.3のSim結果

●入力電圧 では、VinにDCバイアス2.5Vで、振幅が1mVのSin波を入力してみましょう。下記Fig.4で、一番上の波形が、入力電圧です。

●Vbase電圧 Vbase電位は、上から2番目の波形です。入力電圧のバイアス電圧2.5Vでしたが、C1のコンデンサにより、信号のDC成分がカットされ、抵抗分割でバイアスされた約0.579Vを中心に1mVの振幅が出ています。

●出力電圧 出力電圧は、一番下の波形ですが、約2.85Vを中心に約80mVに増幅されています。

以上の結果より、C1により、適切に信号が伝達され、きちんと増幅できたことが確認できました。

Contents:解説3、 エミッタ接地回路のAC解析

次に考えてみたいのは、この回路の周波数特性がどうなっているかということです。

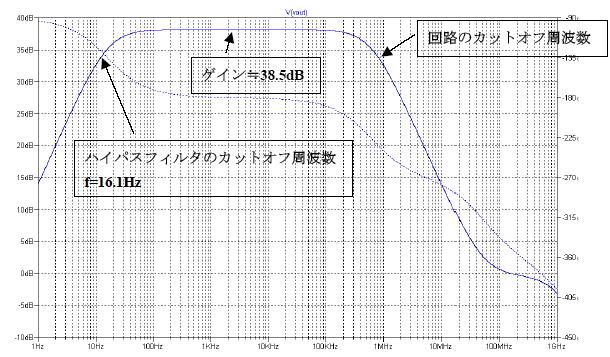

結果を以下のFig.5に示します。

Fig.5、Fig.3のAC解析Sim結果

上記Fig.5から分かりますように、カットオフ周波数が、約16.1Hz以下では、ハイパスフィルタにより、信号が減衰しており、高い周波数だけ信号をパスすることが分かります。更に高い周波数で、ゲインが下がっているのは、このトランジスタ回路で決まるカットオフ周波数によるものです。詳しくは、別のページで説明します。

以上が、エミッタ接地回路の周波数特性です。

では、手で計算した結果と、シミュレーション結果を比べてみましょう。

| パラメータ | 計算 | Sim値 |

| ゲイン | 39.4dB | 38.5dB |

| ハイパスフィルタのカットオフ周波数 | 15.5Hz | 16.1Hz |

手計算では、トランジスタ回路のベース電流の影響を無視したり、出力電圧のバイアス点を電源の1/2において、コレクタ電流を計算しているため、若干の誤差が出たものと考えますが、手計算でもかなり近いところまで、値が算出できていると考えます。

<この回路の注意点>

ここで取り上げた回路は、ディスクリートトランジスタ等でよく構成される回路です。

今回、勉強のために取り上げましたが、実際に半導体回路内で用いるためには、uFオーダーのカップリングコンデンサが必要になる、Vbeのばらつきや、温度変化により、エミッタ電流が変化しやすいなど、IC内部では使いにくいです。あくまで、回路理解のために取り上げているため、ご了承ください。

Contents:今回のポイント

以上、ここでは、エミッタ接地回路の例を挙げ、各種計算を行ってみましたが、ある程度簡単な計算でも十分、各値が計算できることが分かったと思います。いろいろな回路が計算できるようになれば、直感的に、いろいろな特性が分かりやすくなるため、考えられる回路設計の幅も広がります。はじめは、難しいですが、がんばって計算できるようになっていきましょう。

次のページ、エミッタ接地6に進む

戻る

このサイトの内容は趣味で勉強してきたことを応用し、綴っているページです。一般的なことを書いているつもりであり、広告などございますが、あくまで趣味で作っているサイトです。また、特許や商標などは十分調査できていません。また、そういった権利を侵害するつもりもございませんので、万が一そういった場合は削除させていただきますので連絡いただきたいです。また、本ページの内容は実際の動作などを保証するものではございません。使っているツールなども趣味の範囲で使っているため、商用などで利用する場合は注意していただきたいです。また、参考文献などはリンクで表示させていただいております。上記内容につきましては、あらかじめご了承ください。

作者が過去、トランジスタ回路を勉強する場合に、一番役にたった書籍をいくつか紹介します。まだ読まれていない方は、一度チェックしてみてはいかがでしょうか?