アナログ回路を勉強する回路設計のホームページ:http://kaironohanashi.main.jp/index.htmlです。

Transistor Circuits:カレントミラー回路の基本3

今回は、カレントミラー回路の簡単な誤差対策ついて考えてみたいと思います。

Contents:解説1、 カレントミラー回路の誤差対策

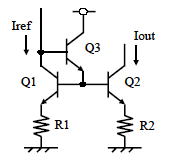

Fig.1 カレントミラー回路1

Fig.1にカレントミラー回路の例を示します。この回路は前節でお話した誤差 1、ベース電流 2、アーリー電圧 この二つを対策した回路です。

1、ベース電流対策 Q3を追加することにより簡易的にベース電流対策ができます。別途詳細の説明はしたいと思いますが、今回は、記事を紹介します。詳しくはシステムLSIのためのアナログ集積回路設計技術〈上〉のP.301等で解説されています。

Contents:解説2、 カレントミラー回路の誤差対策

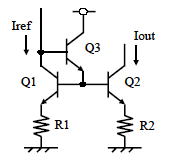

Fig.2 カレントミラー回路1

アーリー電圧対策 R1、R2を追加することにより簡易的にアーリー電圧対策ができます。これはR1、R2を追加することにより、出力インピーダンスが増強できるためです。

詳しくはシステムLSIのためのアナログ集積回路設計技術〈上〉のP.303で解説されています。

Contents:解説3、カレントミラー回路の誤差対策

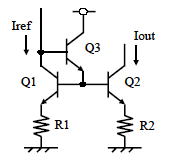

Fig.3 カレントミラー回路1

R1、R2によるVbeばらつき対策。上記1、2以外に実はR1、R2に掛かる電圧を調整することにより Vbeのばらつきも対策できます。例えばVbeのペア性のばらつきが数mVだとするとR1、R2に掛かる電圧をそれより十分高い電圧にすればVbeのばらつきは見えてこないというものです。

Contents:今回のポイント

以上、Fig.1のカレントミラー回路は、1〜3の対策を簡易的に行うことが出来る回路です。これ以外にもさまざまなテクニックが存在しますが、また別途記事を書きたいと思います。カレントミラー回路の動作や計算についても、以下の書籍が詳しいです。

システムLSIのためのアナログ集積回路設計技術〈上〉

戻る

このサイトの内容は趣味で勉強してきたことを応用し、綴っているページです。一般的なことを書いているつもりであり、広告などございますが、あくまで趣味で作っているサイトです。また、特許や商標などは十分調査できていません。また、そういった権利を侵害するつもりもございませんので、万が一そういった場合は削除させていただきますので連絡いただきたいです。また、本ページの内容は実際の動作などを保証するものではございません。使っているツールなども趣味の範囲で使っているため、商用などで利用する場合は注意していただきたいです。また、参考文献などはリンクで表示させていただいております。上記内容につきましては、あらかじめご了承ください。

作者が過去、トランジスタ回路を勉強する場合に、一番役にたった書籍と、簡単にシミュレーションができるようになった書籍を紹介します。まだ読まれていない方は、一度チェックしてみてはいかがでしょうか? |